Триггер что это в электрике

Виды триггеров и особенности их работы

Электроника предполагает точное выполнение заданной программы с учетом текущего состояния всей логической схемы. За часть работы электронной цепи отвечают триггеры. Статья опишет — основные типы триггеров, их устройство и принцип работы, а так же расскажет зачем такие устройства используются в электронных схемах. Отдельно будет описан симметричный триггер.

Определение

Что такое триггер? Триггером называют электронное устройство, обладающее способностью довольно долгое время находиться в 1-ом из 2-х стабильных состояний, а так же чередовать их из-за воздействия какого-то внешнего сигнала. Триггер — это по сути простая электроника, от которой зависит работоспособность более сложных систем

Он способен хранить двоичную информацию (ноль или один) после того, как перестанут действовать входные импульсы. Основное назначение устройства, это переключение из одного состояния в другое. Хранит триггер в своей памяти 1 бит информации, которые и определяют его текущее состояние: логический «0» или логическая «1».

Какие входы есть у триггера? Любой триггер может иметь несколько входов, которые бывают:

Работа устройства строится на 2 элементах «И-НЕ», 2 «ИЛИ-НЕ» и других, некоторые разновидности триггеров работают на логических элементах КМОП, ТТЛ, ЭСЛ. Принцип работы любого триггера зависит от количества входов/выходов, а также от типа самого устройства.

В электронике используются устройства на транзисторах или микросхемах. Транзисторные модели применяются при сложных интегральных схемах старого типа. Логическая микросхема обладает меньшими габаритами, хранит информацию без перегрева и перегрузок. Поэтому их используют в более миниатюрных и сложных цепях современной электроники.

Разновидности

Для того чтобы разобраться как работает триггер, необходимо понять к какому классу и типу он относится. Существуют 2 основных класса этих устройств:

Обе разновидности имеют схожий принцип работы. Отличие заключается только в процессе перехода сигнала из одного состояния в другое. Асинхронные делают это напрямую, а синхронные работают исходя из этого сигнала.

Асинхронные

Асинхронные RS-триггер имеет 2 основных входа «R» и «S». Также предусматриваются выходы «Q» и «Q−». Устройство RS триггера позволяет выполнять следующую последовательность:

Асинхронный RS-триггер условно работает следующим образом:

Схема RS-триггера асинхронного типа самая простая. Она работает без синхронизации с дополнительным входом. Используется RS компонент в простых элементах или как дополнение для более сложных триггеров.

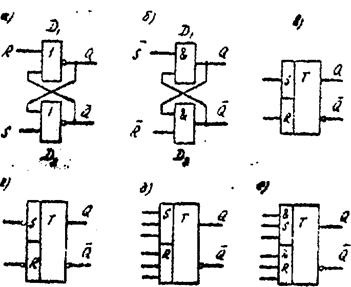

Далее будет представлена УГО, таблица истинности и общая схема такого триггера.

Синхронные

Немного более сложное устройство. Работают с дополнительной синхронизацией сигналов. Эти RS-триггеры также имеют входы «R» и «S», а также выходы «Q» и «Q–». Отличие заключается в наличие синхронизирующего входа «С». Этот контакт нужен для синхронизации входящих сигналов. Называют этот вход «clock» или тактовый. Триггер имеет следующий принцип работы:

Синхронизация используется для снижения части помех. Часто RS-триггеры этого типа используют для цепей с параллельным подключением, значительно снижая помехи от элементов с высокой магнитной индуктивностью.

Графическое обозначение, таблица истинности и диаграмма устойчивых состояний устройства представлена ниже.

Асинхронные и синхронные модели далеко не единственные, которые использует схемотехника для построения логических моделей работы. Далее будут представлены разновидности триггеров с иным принципом работы.

D-триггер

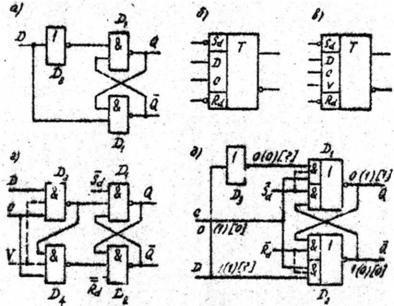

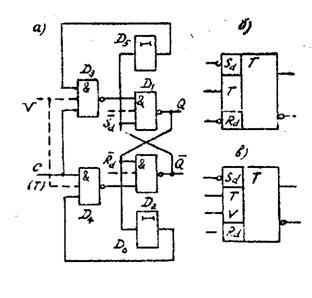

Эти виды простых триггеров так же используют для хранения информации о своем текущем состоянии один бит памяти. Используют его в простых электронных схемах вычислительных устройств и автоматики. Данная модель также относится к синхронному типу и имеет вход «С». Главное отличие заключается в замене 2 входов «R-S» на один контакт «D». Применение всего одного входа и наличие синхронизации позволяет значительно упростить работу устройства. Для работы D-триггера используется следующая схема:

Иными словами, состояние триггера на выходе зависит от его предыдущего положения. Если предыдущее положение было в состоянии высокого напряжения, то на этот выход поступит логическая 1. Если положение было в состоянии сброса, то логический 0.

Практически все D-триггеры являются динамическими. При динамическом управлении состоянием триггера используется понятие фронта. Фронтом называют переход от 1 к 0. Подразумевается 2 вида фронта:

Существуют разновидности D устройств с дополнительным входом V. Название этого входа расшифровывается как проверочный. Работает такой элемент с неким замедлением. Оно необходимо для предварительной синхронизации сигнала, с его последующим подтверждением. При этом не играет особой роли, сколько памяти занято в устройстве. Обычные и DV-триггеры предназначены для работы в сложных устройствах с множеством ячеек. Например, в электронных счетчиках эти устройства отвечают его за актуальное значение. При его смене состояние триггера изменяет свой фронт.

Далее приведена таблица истинности и УГО фронтов.

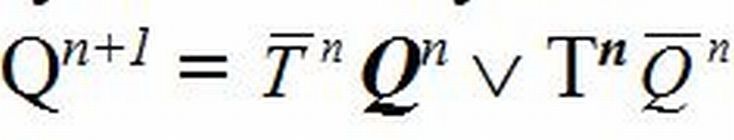

Т-триггер

Триггеры типа T на логических элементах включают в себя многие возможности ранее описанных устройств. Есть модели асинхронного и синхронного типа, динамические и с дополнительным подтверждающим входом.

Асинхронные

При получении положительного сигнала на вход, на выходе получается напряжение в 2 раза выше входного. Такой эффект возможен только при импульсном сигнале, поступающем на T вход. При этом частота поступления по временной шкале не имеет препятствий, а значит сигнал доходит гораздо быстрее. Асинхронные T устройства в состоянии логической 1 на выходе имеют противофазу инверсного выхода.

Синхронные

Эти T-триггеры подобны асинхронным. Исключение состоит в наличие тактового сигнала на входе. Также существует противофаза на инверсном выходе и появление удвоенного напряжения.

Устройство T элементов можно легко отнести к делителям импульсных сигналов. Эти элементы работают только при наличии переднего фронта. Иными словами, осуществляется переход от 0 к 1. Но разница заключается в учете временного интервала между импульсами.

Триггеры типа T часто используются в логических вычислительных процессах. Осуществляется это за счет функции увеличения или снижения напряжения:

При учете, сколько памяти необходимо для перехода и деления сигнала, элемент может быть дополнен входом подтверждения. Программирование с использованием T-триггера допускает использование устройства в различных электронных счетчиках без встроенной памяти. Далее дана диаграмма работы устройства.

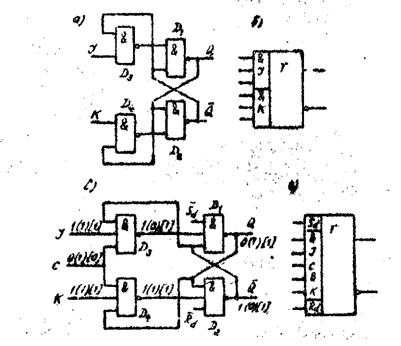

JK-триггер

Является самым универсальным электронным элементом. В этих устройствах присутствуют:

JK устройство работает по принципу перехода из одного состояния в другое, но с учетом единицы времени. Также существует разность при подаче сигнала на вход синхронизации. Иными словами, если на оба входа JK подать логическую 1, то на его выходах появится прямо противоположное значение. Но при этом устройство не воспримет наличие двух 1 единиц как ошибку.

В зависимости от назначения, в данном триггере может использоваться так называемый фронт (передний или задний). В этом случае устройство считается синхронным, а его состояние определяется актуальным положением логических чисел. При расчете рабочего состояния элемента также учитывается возможность одновременного использования устройства в качестве T или D триггера. В этом случае учитывается параметр временного интервала поступления сигнала, какое напряжение будет получено при выходе и устойчивость состояния элемента. Информатика часто использует этот элемент в качестве универсального устройства контроля состояния устойчивой работы простых логических функций. Далее дана диаграмма работы устройства.

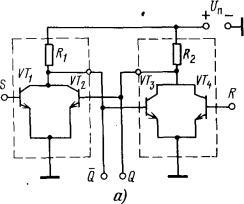

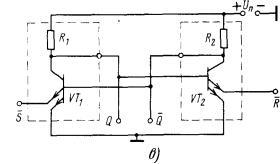

Симметричный

Симметричный триггер относится к особому виду элементов. Он создается на транзисторах и является усилителем постоянного тока двухкаскадного типа. Работает устройство за счет использования транзисторов с полностью идентичными параметрами.

Принцип работы следующий:

При смене положения транзисторов создается перепад напряжения, и оно значительно снижается.

В схемах симметричных триггеров основным элементом является система запуска. Она может отличаться по способу управления и месту, с которого поступил пусковой импульс.

Место поступления импульса может быть от коллектора или базы транзистора. При таких схемах подключения существует вероятность появления ложного или вторичного сигнала. Он отсекается путем подключения диода.

Основным недостатком симметричных элементов является полная зависимость от времени поступления импульсного сигнала и его длительности. Если длительность недостаточная, импульс не успеет открыть транзистор, а значит не произойдет закрытие второго транзистора.

Такие устройства используются в устройствах учета импульсов, генераторах частоты, переключателях радиоэлектронных цепей.

Заключение

С триггерами в жизни мы сталкиваемся довольно часто, ведь они широко используются в различных сферах. В данной статье было приведено описание и области использования различных разновидностей данного устройства. При ремонте электронного оборудования важно знать: для чего нужен этот элемент, где он используется и по какому принципу работают такие устройства.

Видео по теме

Триггеры

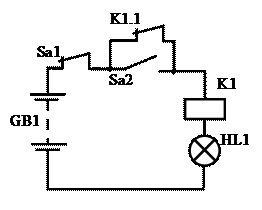

Триггер — электронная схема, имеющая несколько устойчивых состояний, сохраняющихся длительное время (пока включено электропитание схемы). Соответственно триггеры могут выполнять функцию элементов памяти. В цифровой технике используются бистабильные триггеры с двумя устойчивыми состояниями, которые кодируют значения логических «0» и «1». Триггеры могут быть построены на дискретных элементах (транзисторные каскады) и на логических элементах — цифровые триггеры. Также триггер может быть представлен в виде электромеханической аналогии (релейной схемы).

1 Классификация триггеров.

Триггеры различаются по логике работы и по способу приема и запоминания информации. Ниже представлена классификация триггеров, предложенная в книге Е.Угрюмова «Цифровая схемотехника». В ней выделены наиболее популярные типы триггеров, однако количество их разновидностей гораздо больше.

в) По внутренней структуре:

1) Одноступенчатые: в их внутренней структуре одна запоминающая схема, которая переключает свое состояние (запоминает данные) под влиянием управляющих сигналов. По одноступенчатой схеме строятся асинхронные триггеры и синхронные управляемые уровнем.

2) Двухступенчатые (или многоступенчатые) триггеры состоят из двух одноступенчатых триггеров. При переключении двухступенчатого триггера сначала переключается первая, а только следом — вторая. Это позволяет записывать данные только по фронту синхроимпульса, не реагируя на изменения на информационных входах в течении синхроимпульса. Т.е. по многоступенчатой схеме строятся синхронные управляемые фронтом триггеры. Это наиболее применяемый сегодня тип триггеров.

2 Структура триггера.

3. Асинхронные и синхронные управляемые фронтом триггеры

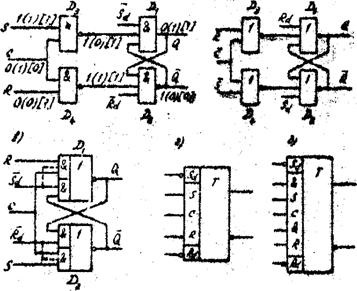

Функционирование и внутренняя схема асинхронного RS — триггера соответствует описанной выше схеме памяти. Данный тип триггера фактически не имеет схемы управления на входе.

Синхронные RS — триггеры с управлением уровнем имеют вход синхронизации (С), сигнал на котором разрешает управление с информационных входов, пока находится в активном состоянии. Входные информационные сигналы «пропускаются» через логические вентили И (для схемы на базе элементов ИЛИ-НЕ, активный уровень (С) = 1) или через вентили ИЛИ (для схемы на базе элементов И-НЕ, активный уровень (С) = 0).

Характерной особенностью триггерных схем, управляемых уровней синхроимпульса, является то, то изменение уровней информационных сигналов в течение действия синхроимпульса приводит к изменению состояния триггера. Если по фронту синхросигнала в триггер было занесено значение «1», и далее в течение удержания активного уровня синхросигнала C информационные сигналы приняли значения R =1, S =0, то это приводит к переключению триггера в состояние «0». Следовательно, для обеспечения работы триггера сигналы R и S должны оставаться неизменными в течении активного уровня синхроимпульса, а изменяться в течение паузы между синхроимпульсами.

Синхронный RS-триггер с управлением по фронту построен по многоступенчатой схеме, описанной ниже.

RS-триггеры редко используются как самостоятельные элементы, но, как говорилось выше, являются элементом памяти (фиксатором) в составе других типов триггеров.

D-триггером (или триггером задержки сигнала) называют триггер с одним информационным входом (D) и входом синхронизации (С). По импульсу синхронизации © состояние на входе (D) сохраняется в триггере и устанавливается на выходе (Q). Состояние выхода Q останется неизменным до следующего импульса на входе синхронизации. Как видно из описания D-триггер является синхронным (обязательно используется сигнал синхронизации). Можно построить также схему асинхронного D-триггера (см. Рисунок 4 а)), но она будет иметь смысл только как повторитель с задержкой на переключение, а не как схема памяти. Асинхронные D-триггеры почти не используются.

Из широко применяемых первый — D-триггер с управлением по уровню, так же называемый «триггер-защелка» (LATCH) (см. Рисунок 4 г). Он прозрачен для входного информационного сигнала пока сигнал синхронизации © в активном состоянии и защелкивает значение на выходе (Q) в момент перехода (С) в неактивное состояние. Такой D-триггер представляет собой RS-триггер с синхронизацией по уровню, у которого на вход S подключен информационный сигнал (D), а на вход ® — инвертированный информационный сигнал. То есть в схему управления добавляется один инвертор «по входу». Входы Rd и Sd используются для асинхронных сброса или установки триггера в определенное состояние и удержание его в этом состоянии, если требуется. Для устойчивой работы такого D-триггера необходимо, чтобы состояние входа D не изменялось в момент действия синхроимпульса на входе С.

Пусть Q = 1, Q`= 0. Поступающий на счетный вход импульс приводит к появлению нулевого сигнала на выходе элемента D4 (на его входах — две «1») и последовательной установке сигналов Q = 1, Q`= 0, т.е. к опрокидыванию триггера в нулевое состояние. При этом сигнал на входе D3 не изменяется, так как на его входе в течение tз действует нулевой сигнал, поступающий с выхода Q` через элемент задержки D5.

После окончания действия счетного импульса сигналы на выходах элементов D3 и D4 принимают единичные значения, а на вход D3 через элемент задержки D5 поступает разрешающий уровень с выхода Q`. В результате следующий счетный импульс перебросит триггер в исходное состояние.

Элементы D5 и D6 обеспечивают задержку появления сигналов обратной связи с тем, чтобы в течение действия счетного импульса не происходило многократного переключения триггера. В интегральных триггерах роль элементов задержки могут выполнять либо логические элементы, либо специальные полупроводниковые приборы с накоплением заряда. Однако, в силу жестких ограничений на длительность импульса на счетном входе и сложности реализации элементов задержки, Т-триггеры на базе RS-триггера с управлением уровнем синхросигнала почти не используются, а применяются триггеры с управлением по фронту синхросигнала.

ТV-триггер является разновидностью Т-триггера с дополнительным входом разрешения счета. Принцип его работы аналогичен DV-триггеру, описанному выше.

Что такое триггер в электронике — подробно разбираемся в терминах

Скорее всего, вам уже приходилось слышать это слово «триггер». Например, вы возможно, обращали внимание на смешные картинки — мемы, на которых в последнее время очень часто встречается это слово. Кроме этого, вы возможно, связываете это понятие с какой-то функцией, запускающей другие события. Но, в данной статье мы подробно поговорить о триггерах в электроники. Триггер это в электронике — устройство, которое в один момент времени может находиться в одном из устойчивых состояний. Обычно, таких состояний существует два. В этой статье мы подробно обсудим принципы работы самых простых типов триггеров — RS. Также, мы коснемся вопроса триггеров счетчиков типа T.

Вам также будет интересно прочитать о принципах работы необычных JK триггеров, о которых мы поговорим во второй части статьи, кстати, именно там мы приведем таблицу перехода данного типа электронных устройств.

Что такое тригеры —кратко

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

| S | R | Q | |

| запрещено | |||

| 1 | 1 | ||

| 1 | 1 | ||

| 1 | 1 | хранение бита | |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 2 10 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

RS-триггер имеет два выхода:

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

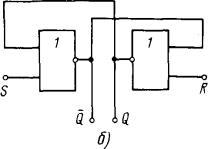

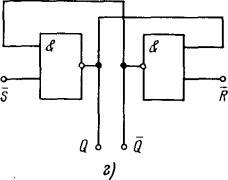

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

D – триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Таблица переходов D-триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

| * | Режим хранения информации | |||

| * | 1 | 1 | ||

| 1 | * | Режим записи информации | ||

| 1 | 1 | * | 1 |

Если на входе D – “1”, то по приходу синхроимпульса Q = 1. Если на D “0”, то Q =0.

Счётный триггер (Т-триггер)

Т-триггер имеет один счётный информационный вход.Триггер переключается каждый раз в противоположное состояние, когда на вход Т поступает управляющий сигнал.

Таблица 2.5 – Таблица переходов Т триггера

| T | Q(t) | Q(t+1) |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

Универсальный триггер (JK-триггер)

Такой триггер имеет информационные входы J и К, которые по своему влиянию аналогичны входам S и R тактируемого RS-триггера:

Но в отличие от синхронного RS-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещённой комбинацией и приводит триггер в противоположное состояние.

Таблица переходов JK триггера

| K | J | C | Q(t) | Q(t+1) |

| 1 | ||||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | |||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 |

Цифровая электроника – ЯБ-триггеры с доминирующим Я-входом

Наличие запрещенных комбинаций для тактируемых &У-триггеров вызвало идею построения триггера, который принудительно устанавливает Qx в 0 при S= 1 и R = 1, при подаче синхроимпульса. Это становится возможным благодаря особенному подключению входов. На рис. 7.35 показано такое соединение входов. При S = 1 и R = 1, 1-сигнал не может воздействовать на триггер, так как на выходе элемента НЕ действует 0. И-элемент запирается. 1-сигнал на R разрешает сброс. Режим установки при S = 1 и R = 0 остается возможен, так как теперь на выходе элемента НЕ действует 1 и И-элемент имеет на выходе 1.

Еще несколько полезных моментов

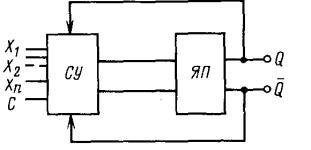

Общие сведения. Помимо логических элементов, реализующих основные логические операции, в цифровой технике широко используются в качестве базовых элементов ячейки памяти на основе разнообразных триггеров. Обобщенная модель триггера показана на рис. 3.6. Очевидно, любой триггер состоит из схемы управления (СУ) и бистабильной ячейки памяти (ЯП). Триггеры имеют входы управляющих сигналов Х1, Х2,…Хn два взаимоинверсных выхода Q и , а также могут иметь вход синхронизации С.

В общем случае к триггерам относят устройства, имеющие два устойчивых состояния, которые устанавливаются при подаче соответствующей комбинации сигналов на управляющие входы и сохраняются в течение заданного времени после окончания действия этих сигналов. Триггеры способны хранить двоичную информацию (состояния «О» и «1») после окончания действия входных импульсов. Это свойство обусловлено тем, что устройством управляют не только внешние сигналы, но и сигналы обратной связи самого триггера.

По функциональному признаку, определяющему поведение триггера при воздействии сигнала управления и способа управления, триггеры подразделяют на следующие типы:

По способу управления триггеры подразделяют на асинхронные и тактируемые. В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах переключение производится только при наличии разрешающего, тактирующего импульса на входе синхронизации.

В зависимости от типа используемых ячеек памяти триггеры подразделяются на статические, статико-динамические и динамические. Первые два типа реализуются на основе логических элементов НЕ, ИЛИ-

НЕ, И-НЕ, а последний на основе МДП транзисторов.

В зависимости от типа базовых логических элементов реализуются триггеры с различными параметрами: быстродействием, потребляемой мощностью, нагрузочной способностью и др.

Как видно из рассмотрения принципиальных схем, основу триггеров составляют два инвертора, связанные между собой взаимными перекрестными связями. Эти связи обусловливают в процессе переключения возникновение положительной обратной связи, способствующей повышению быстродействия и надежности работы схемы.

При наличии логической 1 на выходе одного инвертора на выходе другого поддерживается логический 0. Необходимые уровни напряжения на выходе издаются схемой управления, которая при использовании логических элементов семейства ТЛНС (см. рис. 3.7, а) образована транзисторами VT1 и VT2, а при использовании элементов семейства ТТЛ (см. рис. 3.7, в) образована эмиттерными переходами транзисторов VT1 и VT2. Триггеры, реализованные на основе логических элементов ИЛИ-НЕ, работают в положительной логике, а реализованные на основе логических элементов И-НЕ работают в отрицательной логике. Для работы в положительной логике схема управления последних усложняется добавлением двух инверторов.

Уровни напряжений на обоих выходах триггера различны и одновременно изменяются на противоположные при работе устройства управления. Поэтому на условном обозначении триггера (см. рис. 3.7, б, г) один из выходов обозначен Q, а второй—через (факт инверсии отражается кружком на стороне прямоугольника). Выход Q считается главным: значениями Q характеризуют состояние триггера в целом.

Уравнение состояний RS-триггера имеет вид Здесь индексами n и n+1 обозначены значения величины Q до и после поступления управляющих сигналов. Используя это уравнение, можно определить возможные состояния триггера при разных наборах управляющих сигналов:

если S = 1 и R = 1, то триггер находится в неопределенном состоянии Х, (т.е. с равной вероятностью может находиться в любом из устойчивых состояний Q = 1 или Q = 0), поэтому такой набор является запрещенным: нельзя одновременно подавать на триггер противоположные команды S (установить 1) и R (установить 0).

Наибольшей универсальностью среди триггеров обладает JK-триггер Он работает как RS-триггер, причем в отличие от RS-триггеров здесь допустимо, чтобы оба управляющих сигнала были равны 1.

Если управляющие сигналы J и К равны 1, то JK-триггер работает как T-триггер. При подаче на вход С синхронизирующего импульса триггер будет работать в режиме делителя на 2. Этот режим используется при построении последовательных счетчиков и делителей частоты любой сложности.

Если на информационные входы J и К подавать противофазные логические сигналы, то триггер будет работать в режиме синхронной записи информации. При подаче тактового импульса на вход С эта информация появляется на выходе, т. е. сдвигается в следующую ячейку Такой режим используется при построении сдвигающих регистров, распределителей импульсов, синхронных.

Интегральные JK-триггеры часто имеют несколько управляющих J, К входов, что расширяет его функциональные возможности и позволяет экономить внешние логические элементы. С помощью указанных входов триггер можно установить в определенное состояние независимо от тактового импульса. Поэтому эти входы получили названия предустановки и стирания.

Квазистатические триггеры в отличие от динамических не требуют так называемого «тактового питания» в период хранения информации. При записи информации тактовое питание необходимо, оно осуществляется тактовыми импульсами, имеющими длительность, меньшую, чем постоянная времени заряда и разряда паразитных емкостей затворов МДП транзисторов схемы. По сравнению со схемами статического типа квазистатические и динамические схемы триггеров позволяют в 2—3 раза уменьшить число используемых МДП транзисторов.

В динамических триггерах по истечении времени хранения информация теряется. Для сохранения информации необходимо ее периодическое восстановление путем подачи последовательности внешних импульсов, период которых Т меньше времени хранения информации t. Эти импульсы одновременно выполняют функции синхронизации. В зависимости от числа последовательностей синхроимпульсов различают двух- и четырехфазные динамические элементы.

Характерной особенностью цифровых устройств на основе динамических триггеров является то, что синхронизация в них осуществляется путем подключения и отключения соответствующих элементов к цепи питания. При этом элементы потребляют мощность от источника питания не постоянно, а периодически в течение относительно коротких промежутков времени, когда производится переключение элементов или восстановление информации. В результате устройства на динамических элементах при низких частотах переключения потребляют существенно меньшую мощность, чем на основе статических триггеров. Поэтому динамические триггеры являются весьма перспективными элементами для БИС памяти. Рассмотрим принцип действия динамического триггера, пригодного для использования в качестве ячейки памяти БИС.

На рис. 3.8 изображена схема динамического триггера на основе двух инверторов VT1, VT3 и VT2, VТ4, с взаимными перекрестными связями. В триггере используются МДП транзисторы с каналом р-типа. Питание и синхронизация работы триггера производятся импульсными последовательностями, подаваемыми в разрядные шины РШ и РШ1 (в них потенциалы могут принимать значения –Un, 0 B). Хранение информации обеспечивается паразитными емкостями МДП транзисторов, для удобства обозначенными С1 и С2.

Для записи на адресную шину подают напряжение –Un, а на разрядные шины РШ1 и РШ подают уровни –Un и 0. Уровень –Un через ключ VT4 поступает на вход транзистора VT1 и открывает его. На затвор транзистора VT2 поступает уровень 0, и, следовательно, он закрывается. Напряжение на емкости С1 принимает значение uC1 = –Un, а на емкости С2 равно нулю (иC1=0). После записи отключают напряжение на адресной шине.

Так как остаточный ток закрытого транзистора VT1 мал, то емкость С1 будет сохраняться на выходах ячейки (на стоках VT1 и VT2) длительное время За это время можно несколько раз считывать информацию ячейки (следует учитывать что при считывании приходится открывать транзистор VT4 и разряд С1 ускоряется). Для того чтобы поддерживать напряжение на емкости С1, несмотря на неизбежный ее разряд, осуществляют регенерацию: периодическую запись того же кода.

Скачайте интересную публикацию: Схема устройства трегеров

Динамические триггеры на МДП транзисторах экономичнее и компактнее триггеров на биполярных транзисторах, но уступают им по быстродействию.